# Model Checking a Cache Coherence Protocol of a Java DSM Implementation<sup>\*</sup>

Jun Pang<sup>1</sup>, Wan Fokkink<sup>2,3</sup>, Rutger Hofman<sup>2</sup>, Ronald Veldema<sup>4</sup>

<sup>1</sup> Carl von Ossietzky Universität Oldenburg, Department für Informatik, Ammerländer Heerstraße 114-118, 26111 Oldenburg, Germany email: jun.pang@informatik.uni-oldenburg.de

<sup>2</sup> Vrije Universiteit Amsterdam, Afdeling Informatica, Boelelaan 1081a, 1081 HV Amsterdam, The Netherlands email: {wanf,rutger}@cs.vu.nl

<sup>3</sup> CWI, Software Engineering Department, Kruislaan 413, 1098 SJ Amsterdam, The Netherlands

<sup>4</sup> Friedrich-Alexander-Universität Erlangen-Nürnberg, Institut für Informatik, Martensstr. 3, 91058 Erlangen, Germany email: veldema@cs.fau.de

## Abstract

Jackal is a fine-grained distributed shared memory implementation of the Java programming language. It aims to implement Java's memory model and allows multithreaded Java programs to run unmodified on a distributed memory system. It employs a multiple-writer cache coherence protocol. In this paper, we report on our analysis of this protocol. We present its formal specification in  $\mu$ CRL, and discuss the abstractions that were made to avoid state explosion. Requirements were formulated and model checked with respect to several configurations. Our analysis revealed two errors in the implementation.

$Key\ words:$  formal specification, model checking, cache coherence protocols, Java memory model,  $\mu {\rm CRL}$

<sup>\*</sup> This is the full version of an extended abstract that appeared in the Proceedings of the 8th Workshop on Formal Methods for Parallel Programming: Theory and Applications, IEEE Computer Society Press, 2003. The research is partly supported by the Dutch Technology Foundation STW under the project CES5008.

## 1 Introduction

Shared memory is an attractive programming model for interprocess communication and synchronization in multiprocessor computations. In the past decade, a popular research topic has been the design of systems to provide a shared memory abstraction of physically distributed memory machines. This abstraction, known as Distributed Shared Memory (DSM), has been implemented both in software (e.g., to provide the shared memory programming model on networks of workstations) and in hardware (e.g., using cache coherence protocols to support shared memory across physically distributed main memories).

Multithreading is a programming paradigm for implementing parallel applications on shared memory multiprocessors. It is widely used as a program structuring mechanism and to support efficient parallel computations. It can improve efficiency and performance in an application program by introducing concurrency or parallelism. Java is one of the few programming languages supporting multithreaded programming at the language level.

The Java memory model (JMM) [11] prescribes certain abstract rules that any implementation of Java multithreading must follow. Jackal [30] is a finegrained DSM implementation of the Java programming language. It aims to implement the JMM and allows multithreaded Java programs to run unmodified on DSM. It employs a self-invalidation based, multiple-writer cache coherence protocol, which allows processors to cache a region (i.e., a contiguous block of memory) created on another processor (i.e., the region's home). All threads on one processor share one copy of a cached region. The region's home and the caching processors store this copy at the same virtual address. A cached region copy remains valid for a particular thread until that thread reaches a synchronization point. In Jackal, several optimizations [29,30] improve both sequential and parallel application performance. Among them, *automatic home node migration* reduces the amount of synchronization, by automatically appointing as the region's home a processor that is likely to access this region often.

$\mu$ CRL [13] is a formal language for specifying protocols and distributed systems in an algebraic style. To each  $\mu$ CRL specification there belongs a *labeled* transition system (LTS), in which the edges between states are labeled with actions. The  $\mu$ CRL tool set [3] can be used in combination with the Construction and Analysis of Distributed Processes toolbox (CADP) [10] to generate, visualize and analyze this LTS. For example, one can detect deadlocks and livelocks, or check the validity of temporal logic formulas [7].

In this paper, we present our formal analysis of a cache coherence protocol

for Jackal using the  $\mu$ CRL tool set and CADP. A  $\mu$ CRL specification of the protocol (including automatic home node migration) was extracted from an informal (C language-like) description of the protocol. To avoid state explosion, we made certain abstractions with respect to the protocol's implementation. Requirements were verified by the  $\mu$ CRL tool set together with CADP. Our analysis revealed many inconsistencies between the description and the implementation. We found two errors in the description (see Section 6.2). The developers of the protocol checked the two errors and found their way in the implementation. Both errors can happen when a thread is writing to a region from remote (i.e., the thread does not run on the home of the region). During the thread's waiting for a lock or an up-to-date copy of the region, the home node may migrate to the thread's processor, so that the thread actually accesses the region at home. The first error resulted into a deadlock. The second error was found when model checking the property of only one home for each region. After updating our formal specification, the requirements were successfully checked on several configurations. Our solutions to the errors were adapted in the implementation of the protocol. The interested readers can find the Jackal distribution (version Beta 1.0) at http://www2.informatik.uni-erlangen. de/Personen/veldema/privat/jackal\_distribution.html.

We summarize our contributions as follows:

- We developed a formal specification of a cache coherence protocol for a Java DSM implementation.

- We found errors both in the description and the implementation, which helped to improve the design and implementation of this protocol.

- This is the most complicated cache coherence protocol to date that has been formally specified and analyzed using model checking.

Outline of the paper. The remainder of this paper is structured as follows. In Section 2, we discuss related work on analyzing the JMM or its replacement proposal and verifying cache coherence protocols using formal techniques. An informal description of the JMM is given in Section 3. Section 4 presents the Jackal system and its cache coherence protocol. In Section 5,  $\mu$ CRL specifications for each component of the protocol are given. Section 6 focuses on our model checking analysis in  $\mu$ CRL. Conclusions are presented in Section 7.

## 2 Related Work

The use of formal methods to analyze the JMM is an active research topic. In [26], the authors developed a formal executable specification of the JMM [11]. Their specification is operational and uses guarded commands. This model

can be used to verify popular software construction idioms for multithreaded Java. In [31], the Mur $\phi$  verification system was applied to study the CRF memory mode [20]. A suite of test programs was designed to reveal pivotal properties of the model. This approach was also applied to Manson and Pugh's proposal [21] by the same authors [32]. Two proofs of the correctness for Cachet [27], an adaptive cache coherence protocol, were presented in [28]. Each proof demonstrates soundness (conformance to the CRF memory model) and liveness. One proof is manual, based on a term-rewriting system definition; the other is machine-assisted, based on a TLA formulation and using the theorem prover PVS. Similar to [31,32], we use formal specification and model checking techniques. A major difference is that we analyzed a cache coherence protocol within a Java DSM system that is already implemented and far more complicated than the abstract memory models analyzed in [26,28,31,32]. Our analysis helped to improve the actual design and implementation of the protocol.

Our work is also related to the verification of cache coherence protocols. Formal methods have been successfully applied in the automated verification of cache coherence on sequentially consistent systems [18], e.g. [6,8,16]. Coherence in shared memory multiprocessors is much more difficult to verify. Recently, Pong and Dubois [24] used their state-based tool for the verification of a delayed protocol [9], which is an aggressive protocol for relaxed memory models. We encountered the same difficulties as [24], such as that the hardware to model is complex, and that the properties of the protocol are hard to formulate. Differences between our work and [24] are: we analyzed a protocol designed for *distributed* shared memory machines; and the protocol supports *multithreaded* Java programs, which makes matters more complicated.

## 3 Java Memory Model

The Java language supports multithreaded programming, where threads can interact among themselves via read/write of shared data. The JMM prescribes certain abstract rules that any implementation of Java multithreading must follow. We briefly present the JMM as given in [11].

We assume a multiprocessor setting, where each processor owns a collection of regions, which are contiguous blocks of memory that contain either a single object or a fixed-size partition of an array. Each thread runs on exactly one processor, and can only access the regions that reside at its processor.

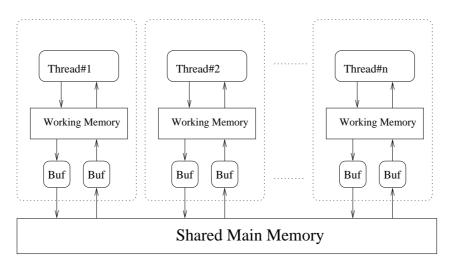

The JMM allows each thread to cache regions in its working memory, which keeps its own working copy of the regions. A thread can only manipulate the regions in its working memory, which is inaccessible to other threads. The

Fig. 1. JMM memory system

working memories are caches of a single main memory, which is shared by all threads. Main memory keeps the main copy of every region. This memory structure is depicted in Fig. 1. A thread's working memory must be flushed to main memory at each synchronization point, which is a lock (unlock) operation that corresponds to the entry (exit) of a synchronized block of code.

The JMM defines a set of actions that a thread may use to interact with memory. Each thread invokes four actions: use, assign, lock and unlock. Four more actions, read, load, store and write, are invoked in case of a multithreaded implementation, following the temporal ordering constraints in the JMM ([11, Chapter 17]). The meaning of each action is as follows:

- (1) use: Read from the working memory of a region.

- (2) assign: Write into the working memory of a region.

- (3) read: Initiate reading from the main memory of a region.

- (4) *load*: Complete reading from the main memory of a region.

- (5) *store*: Initiate writing the working memory into the main memory of a region.

- (6) *write*: Complete writing the working memory into the main memory of a region.

- (7) *lock*: Get the values in the main memory transferred to a thread's working memory through *read* and *load* actions.

- (8) *unlock*: Put the values a thread holds in its working memory back to the main memory through *store* and *write* actions.

Since threads can access regions from different processors, a region's home acts as the region's lock manager. To acquire a lock, a thread sends a lock request message to the lock manager and waits. If the lock is available, the lock manager replies with a notify message; otherwise, the thread needs to wait for the lock to be released. To unlock, the lock holder sends an unlock message to the lock manager.

There were several problems in the original JMM [11]. A detailed discussion of the various problems in the original JMM can be found at http: //www.cs.umd.edu/~pugh/java/memoryModel/. Two replacement semantics for the JMM have been proposed, by Manson and Pugh [21] and by Maessen, Arvind and Shen [20]. A revision of the JMM, called JSR 133, was released in September 2004. Jackal, which will be described in the next section, implements the memory model in JSR 133.

## 4 Jackal DSM System

Jackal [30] is a fine-grained DSM implementation of the Java programming language. It allows multithreaded Java programs to run unmodified on a distributed memory system. Its runtime system implements a self-invalidation based, multiple-writer cache coherence protocol for regions.

The Jackal memory model allows processors to cache a region created on another processor. All threads on one processor share one copy of a cached region. The region's home and the caching processors all store this copy at the same virtual address. The protocol is based on self-invalidation, which means the cached copy of a region remains valid until the thread itself invalidates the copy, which occurs whenever it reaches a synchronization point. Jackal combines features of HLRC [33] and TreadMarks [17]. As in HLRC, modifications are flushed to a home node; as in TreadMarks, twinning and diffing is used to allow concurrent writes to shared data. Unlike TreadMarks, Jackal uses software access checks inserted before each object usage to detect non-local or stable data. Several optimizations were made to improve both sequential and parallel application performance [29,30].

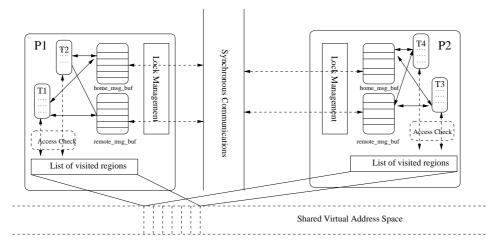

Fig. 2 shows the various components and their interactions in Jackal's cache coherence protocol. P1,P2 are identities of processors, and T1,T2,T3,T4 identities of threads. This picture will be explained in the remainder of this section.

#### 4.1 Address space management

Jackal stores all regions in a single, shared virtual address space. Each region occupies the same virtual address range on all processors that store a copy of the region. Regions are named and accessed through their virtual address. Each processor owns part of the physical memory and creates objects and arrays in its own part. In this way, each processor can allocate objects without synchronizing with other processors. When a thread wishes to access a region created by another processor, it must potentially allocate physical memory

Fig. 2. Components in the Jackal architecture

for the virtual memory pages in which the object is stored, and retrieve an up-to-date copy of the region from its home node. If a processor runs out of free physical memory, it initiates a global garbage collection that frees both Java objects and physical memory pages.

To implement self-invalidation, each thread keeps track of the regions it accessed and cached since its last synchronization point. The data structure storing this information is called a *flush list*. At a synchronization point, all regions in the thread's flush list are invalidated for that thread, by writing *diffs* back to their home nodes. A diff contains the difference between a region's object data and its twin data.

Jackal performs a software access check for every use of a region. The access check determines whether the region referenced by a given pointer contains a valid local copy. Whenever an access check detects an invalid local copy, the runtime system contacts the region's home. It asks the home node for a copy of the region and stores this copy at the same virtual address as at the home node. The thread requesting the region receives a pointer to that region and adds it to its flush list. This flush list is similar to the working memory in the JMM.

#### 4.2 Automatic home node migration

Java programs do not indicate which locks protect which data items. This makes it difficult to combine data and synchronization traffic. Jackal may have to communicate multiple times to acquire a lock, to access the data protected by the lock and to release the lock. The home of a region acts as the manager of the lock (see Section 4.5). To decrease synchronization traffic, automatic home node migration has been implemented in Jackal. It means that Jackal

may automatically appoint as the region's home a processor that is likely to access this region often. This optimization is triggered during the following two cases.

- (1) A thread writes to a region, and an access check detects an invalid local copy; the runtime system contacts the region's home, and finds that the thread's processor is the only one from which threads are writing to this region. Then the home of this region migrates to the thread's processor.

- (2) A thread flushes at a synchronization point, and there is only one processor left from which threads are writing to some region. Then the home of this region migrates to this processor.

Jackal can detect these situations at runtime, and thus reduce synchronization traffic. Automatic home node migration complicates meeting the requirements in Section 6.1.

## 4.3 Regions

In Jackal, a region contains the following information.

- (1) Location: A processor's identity, denoting at which node the region (or a copy) is.

- (2) Home: A processor's identity, denoting the home node for this region.

- (3) State: A region can evolve into four kinds of states. When no thread uses this region, the state of the region is *Unused*; if a region is only used by threads on its home node, its state is *Homeonly*; when this region is only read by threads, its state is *Readonly*; in all other cases, the state of a region is *Shared*.

- (4) WriterList: A list of processors' identities containing threads that are writing or recently wrote to this region. It is only maintained at the home node.

- (5) ReaderList: A list of processors' identities containing threads that are reading or recently read this region. It is only maintained at the home node.

- (6) Object data: An array of bytes.

- (7) Twin data: An array of bytes. It is a copy of the object data for diffing at non-home nodes; initially it is null.

- (8) Localthreads: A natural number, the number of threads accessing this region at the location of the region.

#### 4.4 Messages

Four types of messages can be delivered to a processor.

- (1) Data Request: This message is sent when a thread starts writing to a region from remote. When a processor gets this message, and it is the home of the region, it adds the thread's processor into the WriterList of the region and sends back an up-to-date copy of the region to the thread's processor by a Data Return message. If it is not the home of the region (meaning that the region migrated its home in the meantime), it forwards the Data Request message to the region's new home.

- (2) Data Return: This message is received by a processor when an up-todate copy of a region has arrived. The processor updates the object and twin data of the region. Moreover, this message can also be a home node migration message. If this is the case, then the processor becomes the home of this region, and starts maintaining the WriterList and the state of the region.

- (3) Flush Request: This message is sent when a thread flushes from remote. When a processor gets this request, and it is the home of the region, it mat remove the thread's processor from the WriterList of the region, if the thread was the only one on its processor that was writing to this region. Moreover, it may send a home node migration message to a new home of this region (by a *Region Sponmigrate* message); this happens when there is only one processor left in the region's WriterList. When it is not the home of the region, it simply forwards the *Flush Request* message to the region's new home.

- (4) *Region Sponmigrate*: When a processor gets this message, it becomes the home of the region in question.

Each processor maintains two message queues to store incoming messages. The *HomeQueue* is designed to buffer messages containing a request, while the *RemoteQueue* buffers messages containing a reply.

## 4.5 Locks

Locks guarantee exclusivity when threads write to or flush a region. A processor acts as the lock manager of its regions and region copies. There are five types of locks for each processor: *homequeue*, *remotequeue*, *server*, *fault* and *flush*.

The homequeue lock and remotequeue lock are needed to make sure that the handling of a popped message from a HomeQueue or a RemoteQueue by its processor is completed before the next message is popped from the queue. Jackal's cache coherence protocol allows writes to a region at home and from remote to happen concurrently. The server lock, fault lock and flush lock ensure exclusivity between threads at a processor. The server lock and flush lock must be mutually exclusive for the home of a region, to protect the integrity of region data values and other region information; likewise, the fault lock and flush lock must be mutually exclusive for non-home nodes of a region. When a thread writes at home or from remote, the server lock or fault lock of the thread's processor is needed, respectively. When a thread flushes, the flush lock of its processor is needed. When a lock is released, the lock manager notifies a thread according to the following rules. They are applied in the given order.

- If both the flush and the homequeue lock are available, and there are threads waiting for the homequeue lock or the server lock, one of those threads is notified.

- If both the flush and the remotequeue lock are available, and there are threads waiting for the remotequeue lock, one of those threads is notified.

- If the flush, homequeue and remotequeue lock are available, no threads waiting for either homequeue lock or remotequeue lock, and there are threads waiting for the flush lock, one of those threads is notified.

- If both the flush and the homequeue lock are available, and no threads are waiting for either the homequeue or the remotequeue lock, and there are threads waiting for the fault lock, one of those threads is notified.

- In all other cases, no waiting thread is notified.

## 4.6 Other features

To improve performance, a source-level global optimization *object-graph ag*gregation, and runtime optimization *adaptive lazy flushing*, are implemented in Jackal. These features are not included in our  $\mu$ CRL specification of Jackal's cache coherence protocol, which will be described in Section 5.

The Jackal compiler can detect situations where an access to some object (called root object) is always followed by accesses to subobjects. In that case, the system views the root object and the subobjects as an object graph. Jackal attempts to aggregate all access checks on objects in such a graph into a single access check on the graph's root object. If this check fails, the entire object graph is fetched, which can reduce the number of network round-trips. We did not model object-graph aggregation, because we modeled memory at a rather abstract level.

The Jackal cache coherence protocol invalidates all data in a thread's working memory at each synchronization point. That is, the protocol exactly follows the specification of the JMM, which potentially leads to much interprocessor communication. Due to adaptive lazy flushing, it is not necessary to invalidate and flush a region that is accessed by only a single processor or that is only read by its accessing threads. We did not model adaptive lazy flushing, since it is not relevant for the requirements that we formulated.

## 5 $\mu$ CRL Specification of the Protocol

In this section, we present a formal specification of Jackal's cache coherence protocol in  $\mu$ CRL and verify some general requirements at the behavioral level.

#### 5.1 $\mu CRL$

$\mu$ CRL is a language for specifying distributed systems and protocols in an algebraic style. It is based on the *process algebra* ACP [1] extended with equational abstract data types [19]. The syntax and semantics of  $\mu$ CRL are given in [13,15]. A  $\mu$ CRL specification consists of two parts: one part specifies the data types, the other part specifies the processes.

The data part contains equational specifications; one can declare sorts and functions working upon these sorts, and describe the meaning of these functions by equations. Since booleans are used in the conditional construct of process descriptions, the sort *Bool* must be included in every  $\mu$ CRL specification. Besides the declaration of the sort *Bool*, it is also obligatory that T (true) and F (false) are declared in every specification and that  $T \neq F$ .

Processes are represented by process terms. Process terms consist of action names and recursion variables with zero or more data parameters, combined with process-algebraic operators. Actions and recursion variables carry zero or more data parameters. Intuitively, an action can execute itself, after which it terminates successfully. There are two predefined actions:  $\delta$  represents deadlock,  $\tau$  the internal action. p.q denotes sequential composition, it first executes p and then q. p+q denotes non-deterministic choice, meaning that it can behave as p or q. Summation  $\sum_{d:D} p(d)$  provides the possibly infinite choice over a data type D. The conditional construct  $p \lhd b \triangleright q$ , with b a boolean data term, behaves as p if b and as q if not b.

For example, let  $S: Natural \rightarrow Natural$  be the successor function on natural numbers. Given the recursive equation X(n:Natural)=a(n).X(S(n)), the process X(0) performs the sequence of actions  $a(0).a(S(0)).a(S(S(0))).\cdots$ . And given the recursive equation  $Y=\sum_{n:Natural} a(n).Y$ , the process Y can perform any action a(n) and return to the process Y.

Parallel composition  $\mathbf{p} \| \mathbf{q}$  interleaves the actions of  $\mathbf{p}$  and  $\mathbf{q}$ ; moreover, actions from  $\mathbf{p}$  and  $\mathbf{q}$  may synchronize into a communication action, when this is explicitly allowed by a predefined communication function. In this paper we take as naming convention that for each send action s\_name there is a receive action r\_name, and that they communicate to the action c\_name. Two actions can only synchronize if their data parameters are the same, which means that communication can be used to capture data transfer from one process to another. If two actions are able to synchronize, then in general we only want these actions to occur in communication with each other, and not on their own. This can be enforced by the encapsulation operator  $\partial_H(\mathbf{p})$ , which renames all occurrences in  $\mathbf{p}$  of actions from the set H into  $\delta$ . Additionally, the hiding operator  $\tau_I(\mathbf{p})$  turns all occurrences in  $\mathbf{p}$  of actions from the set Iinto  $\tau$ .

The  $\mu$ CRL tool set [3] is a collection of tools for analyzing and manipulating  $\mu$ CRL specifications, based on term rewriting and linearization techniques [14]. The  $\mu$ CRL tool set, together with the CADP tool set [10], which acts as a back-end for the  $\mu$ CRL tool set, features visualization, simulation, LTS generation, model checking, theorem proving and statebit hashing capabilities.  $\mu$ CRL and its tool set have been successfully used to analyze a wide range of protocols and distributed systems (e.g., [2,12,23]).

## 5.2 Specification of the protocol

The starting point of verifying a system with  $\mu$ CRL is to give an algebraic specification. This generally involves identifying the key behaviors of the protocol components and understanding the way how each component communicates with others.

The cache coherence protocol in Jackal is more complex than an interleaved execution of the threads, where each thread executes in program order. The permitted set of execution traces is a superset of the simple interleaved execution of the individual threads. Furthermore, the  $\mu$ CRL specification is an exhaustive nondeterministic description of the cache coherence protocol. This may lead to state explosion. To deal with this problem, we made some abstractions of each component. In the following discussion, we present the  $\mu$ CRL specification of each component, together with the abstractions we made. For the sake of presentation, we only give parts of the specification to illuminate the crucial points, and omit the specification of data types. The complete specification can be found in Appendix A, which already includes our solutions to the found problems in Section 6 and the additional actions for checking the requirements.

Our model of the cache coherence protocol is a parallel composition of the threads, processors, regions, lock managers and message queues. The complete  $\mu$ CRL specification of this protocol consists of around 1000 lines.

## 5.2.1 Assertions from the developers

The developers added many assertions into the description and required that the protocol should not violate any of them. The assertions are modeled as a part of the  $\mu$ CRL specification. They can be divided into two classes: *order assertions* and *preconditions*.

- Order assertions: This class of assertions imposes a certain order on the usage of the system resources. For example, when a thread performs an action on a region, the corresponding lock should already be held by the thread. Order assertions are modeled in the  $\mu$ CRL specification by imposing a certain order on the execution of actions. For example, the behavior of a thread is modeled like this: only after a thread has taken the server lock of the thread's processor (either immediately by an action r\_nodelay\_serverwait, or after a delay by an action r\_delay\_serverwait), the thread can access a region at home.

- Preconditions: This class of assertions requires that only when a certain precondition is satisfied, the description after it can be executed. For example, only under certain conditions (see Section 4.2) the home of the region automatically migrates. Preconditions are modeled in the  $\mu$ CRL specification as boolean terms in conditional expressions.

## 5.2.2 Regions

In  $\mu$ CRL, each region is modeled as a separate component. It consists of an identity rid, a processor identity pid indicating where the region is, and its information r meaning its home, state, WriterList, and the number of local threads that are writing to this region.

We did not model object and twin data, since they are not relevant to our requirements for the protocol (see Section 6.1). So in our model a thread cannot write any value to a region. Still, when a thread flushes a region from remote, a message (without a diff) is sent back to the home of this region to release the obtained lock (see Section 5.2.3).

The behavior of reading from a region is part of the behavior of writing to a region, in the sense that if needed an up-to-date copy of the region has to be obtained. On top of this, in case of writing, coherence of the region's data is at stake, and at a synchronization point the adapted region must be flushed back to main memory. Thus writing is far more critical for the correctness of the

Table 1 Specification of a region

% pid indicates where the region is; rid is the region's identity; % r contains the region's information. Region(pid:Processorld, rid: RegionId, r:RegionInfo) = % Communication with threads.  $\sum_{tid:ThreadId}$  r\_threadrequestinfo(tid,pid,rid,r). (r\_threadnorefresh(tid,pid,rid).Region(pid,rid,r)  $+\sum_{r':RegionInfo}$  r\_threadrefresh(tid,pid,rid,r').Region(pid,rid,r')) % Communication with processors. + r\_processorrequestinfo(pid,rid,r). (r\_processornorefresh(pid,rid).Region(pid,rid,r').Region(pid,rid,r'))  $+\sum_{r':RegionInfo}$  r\_processorrefresh(pid,rid,r').Region(pid,rid,r'))

protocol than reading. Therefore we abstracted away from the read action of threads. So a region has only two states; we kept the *Unused* state, while the other three states are covered by a single state *Used*. Furthermore, a region only needs to maintain the WriterList.

The  $\mu$ CRL specification of a region is presented in Table 1. We use synchronized actions to ensure that during an access of a thread to a region, no other threads can change the information of this region. This can ensure that a thread or a processor gets the latest status of the region. For instance, in Table 3, a thread gets the information of a region by performing a send action s\_threadrequestinfo, and no access to this region by another thread is allowed until the thread executes a send action s\_threadnorefresh (if it changed nothing) or s\_threadrefresh (if it updated some information of the region). The corresponding actions, which synchronize with the three aforementioned actions (i.e., r\_threadrequestinfo, r\_threadnorefresh and r\_threadrefresh) occur in Table 1. Likewise for processors; see Tables 7 and 8 for occurrences of the actions that synchronize with r\_processorrequestinfo, r\_processornorefresh and r\_processorrefresh in Table 1.

## 5.2.3 Threads

In the  $\mu$ CRL specification, each thread is modeled as a separate process with a unique identity tid (see Table 2). It contains a parameter pid to indicate on which processor the thread executes. Each thread maintains a *FlushList* of identities of regions that it is writing or recently wrote to, to remember that they need to be flushed in the future. It can perform actions write(tid,rid) to start writing to a region with identity rid, and flush(tid) to start invalidating all the regions in its FlushList, if its FlushList is not empty. Table 2Specification of a thread starting to write or flush

Thread(tid:ThreadId, pid:ProcessorId, FlushList:RegionIdSet) =  $\sum_{i=1}^{n} \frac{1}{i} \frac{1}{i} \frac{1}{i} \sum_{i=1}^{n} \frac{1}{i} \frac{1}{i} \sum_{i=1}^{n} \frac{1}{i} \frac{1}{i} \sum_{i=1}^{n} \frac{1}{i} \frac{1}{i} \sum_{i=1}^{n} \frac{1}{i} \sum$

$\frac{\sum_{\mathsf{rid:RegionId}}\mathsf{write}(\mathsf{tid},\mathsf{rid}).\mathsf{ThreadWrite}(\mathsf{tid},\mathsf{pid},\mathsf{rid},\mathsf{FlushList})}{+}$

$\mathsf{flush}(\mathsf{tid}).\mathsf{ThreadInvalidate}(\mathsf{tid},\mathsf{pid},\mathsf{FlushList}) \lhd \mathsf{not}(\mathsf{empty}(\mathsf{FlushList})) \rhd \delta$

Table 3

Specification of a thread starting to write to a region

| $\label{eq:threadWrite} ThreadId, pid: ProcessorId, rid: RegionId, FlushList: RegionIdSet) =$ |

|-----------------------------------------------------------------------------------------------|

| % The thread is already writing to the region.                                                |

| % writeover(tid, rid) will be added here for our verification purpose.                        |

| Thread(tid,pid,FlushList)                                                                     |

| $\triangleleft test(rid,FlushList) \vartriangleright$                                         |

| % The thread must obtain an up-to-date copy of the region.                                    |

| $\sum_{r:RegionInfo}$ s_threadrequestinfo(tid,pid,rid,r).                                     |

| % Write to the region at home if pid is the home of the region.                               |

| $(s\_threadnorefresh(tid,pid,rid).WriteHome(tid,pid,rid,insert(rid,FlushList))$               |

| $\lhd eq(gethome(r), pid) \triangleright$                                                     |

| % Otherwise, write to the region from remote.                                                 |

| ${\tt s\_threadnorefresh(tid,pid,rid)}. WriteRemote(tid,pid,rid,insert(rid,FlushList)))$      |

|                                                                                               |

When a thread starts writing to a region (see Table 3), the corresponding access check determines whether the thread is already writing to the region  $(\mathsf{test}(\mathsf{rid},\mathsf{FlushList}))$ . If not, then first an up-to-date copy of the region must be obtained from the region's home. This access check will also determine whether the thread writes to this region at home or from remote, depending on whether the region's home is the thread's processor ( $\mathsf{eq}(\mathsf{gethome}(\mathsf{r}),\mathsf{pid})$ ). In the first case the server lock is needed if the thread runs on the region's home; in the second case the fault lock of the thread's processor must be acquired.

Table 4 specifies a thread starting to write to a region from remote. The fault lock is acquired (s\_require\_faultlock) from the thread's processor. When the fault lock is granted, either immediately (r\_nodelay\_faultwait) or after the lock has been released (r\_delay\_faultwait) by some other thread, the thread sends a *Data Request* message (s\_thread\_datarequest) to the home of the region (by s\_threadrequestinfo it gets to know the home). The thread waits until it receives a message (r\_signal), which means that the region (local copy, located at the thread's processor) has become consistent with the region at the region's home. Then the thread gets the information of the up-to-date copy of the region (s\_threadrequestinfo), it continues writing to/updating the region (s\_threadrefresh), increases the local thread number by one, and finally releases

Table 4

Specification of a thread writing to a region from remote

| WriteRemote(tid:ThreadId, pid:ProcessorId, rid:RegionId, FlushList:RegionIdSet) = % Thread writes from remote, requires a fault lock, |

|---------------------------------------------------------------------------------------------------------------------------------------|

| % and asks for a fresh copy of the region.                                                                                            |

| s_require_faultlock(pid).                                                                                                             |

| (r_nodelay_faultwait(pid)+r_delay_faultwait(pid)).                                                                                    |

| % Ask for a fresh copy of the region.                                                                                                 |

| $\sum_{r:RegionInfo}$ s_threadrequestinfo(tid,pid,rid,r).                                                                             |

| s_thread_datarequest(tid,pid,gethome(r),rid).                                                                                         |

| s_threadnorefresh(tid,pid,rid).                                                                                                       |

| % Copy arrives, the thread is notified.                                                                                               |

| $\sum_{pid':ProcessorId}$ r_signal(tid,pid',rid).                                                                                     |

| $\sum_{r':RegionInfo}$ s_threadrequestinfo(tid,pid,rid,r').                                                                           |

| s_threadrefresh(tid,pid,rid,increaselocalthreads(r')).                                                                                |

| s_free_faultlock(pid).                                                                                                                |

| % writeover(tid, rid) will be added here for our verification purpose.                                                                |

| Thread(tid,pid,FlushList)                                                                                                             |

|                                                                                                                                       |

the lock by sending an unlock message (s\_free\_faultlock) to the lock manager (see Table 11).

The specification of a thread writing to a region at home, which is omitted here, is similar to the one for a thread writing to a region from remote. Instead of a fault lock, the thread needs to acquire a server lock (s\_require\_serverlock). Once a server lock is granted, either immediately (r\_nodelay\_serverwait) or after the lock has been released (r\_delay\_serverwait), the thread gets the information of the region, and updates the region. Finally it releases the server lock by sending an unlock message (s\_free\_serverlock) to the lock manager.

When a thread invalidates (see Table 5), it empties its FlushList by flushing and removing each region's identity in its FlushList. Similar to the case when a thread writes to a region, a thread can flush a region at home or from remote, depending on whether the region's home is the thread's processor. The flush lock of the thread's processor is acquired before invalidating (s\_require\_flushlock). If the thread invalidates a region from remote (see Table 6), it sends a *Flush Request* message to the home of the region (s\_thread\_flushrequest). If the thread is the only local thread which was accessing the region, the home of the region will need to remove the thread's processor from the region's WriterList. This information is forwarded to the home of the region by setting the last boolean variable in the *Flush Request* message to true. Otherwise, the boolean variable is set to false. The thread updates the information of the local copy of the region by decreasing the parameter *Localthreads* for this region by one. The thread releases the flush lock

Table 5

Specification of a thread invalidating

| ThreadInvalidate(tid:ThreadId, pid:ProcessorId, FlushList:RegionIdSet) = % If FlushList is empty, do nothing. |

|---------------------------------------------------------------------------------------------------------------|

| % flushover(tid) will be added here for our verification purpose.                                             |

|                                                                                                               |

| Thread(tid,pid,FlushList)                                                                                     |

| $\lhd empty(FlushList) \vartriangleright$                                                                     |

| % Thread requires a flush lock.                                                                               |

| s_require_flushlock(pid).                                                                                     |

| $(r\_nodelay\_flushwait(pid)+r\_delay\_flushwait(pid)).$                                                      |

| % The thread gets the status of the first region in the FlushList.                                            |

| $\sum_{r:RegionInfo}$ s_threadrequestinfo(tid,pid,head(FlushList),r).                                         |

| % Invalidate at home.                                                                                         |

| (FlushHome(tid,pid,head(FlushList),tail(FlushList),r)                                                         |

| ⊲ eq(gethome(r),pid) >                                                                                        |

| % Otherwise, invalidate from remote.                                                                          |

| FlushRemote(tid,pid,head(FlushList),tail(FlushList),r))                                                       |

|                                                                                                               |

(s\_free\_flushlock), and waits until it gets a message (r\_signal) indicating that the home of the region has finished with the *Flush Request* message. Then the thread continues to flush other regions in its FlushList, if this list is not yet empty. In the actual protocol, the *Flush Request* message also contains a diff with the difference between the region's object and twin data; we recall that the  $\mu$ CRL specification abstracts away from object and twin data.

The specification of a thread flushing a region at home, which is omitted here, is similar to the one for a thread flushing a region from remote. The difference is that the home of the region also takes charge of automatic home node migration (see Section 4.2). The thread updates the information of the region by decreasing *Localthreads* for this region by one. If the thread is the only local thread which was accessing the region (i.e., if *Localthreads* for this region becomes zero), then the thread's processor is removed from the region's WriterList. If there is only one other processor left in the region's WriterList, the home of the region will migrate to that processor.

Note that the corresponding parts of ThreadWrite, WriteRemote and ThreadInvalidate in the appendix have extra actions writeover(tid,rid) and flushover(tid). These two actions were added to indicate that a thread has completed its action, in order to verify some interested properties. Also note that the corresponding part of WriteRemote in the appendix has already contained a solution to a deadlock found during our analysis of the protocol. The solution requires the thread to perform one extra access check after it receives a notification message r\_signal. More explanation can be found in Section 6.2. Table 6

Specification of a thread flushing a region from remote FlushRemote(tid:ThreadId,pid:ProcessorId,rid:RegionId, FlushList:RegionIdSet,r:RegionInfo) = % Decrease Localthreads for rid. If no other thread is using this region, % this is remembered by setting the last boolean parameter to true, % the region state is set to Unused. (s\_thread\_flushrequest(tid,pid,gethome(r),rid,r,T). s\_threadrefresh(tid,pid,rid,setstate(decreaselocalthreads(r),Unused))  $\triangleleft$  eq(getlocalthreads(r),1)  $\triangleright$ s\_thread\_flushrequest(tid,pid,gethome(r),rid,r,F). s\_threadrefresh(tid,pid,rid,decreaselocalthreads(r))). % Thread releases the flush lock. s\_free\_flushlock(pid). % This invalidation is finished, the thread is notified.  $\sum_{pid':ProcessorId}$  r\_signal(tid,pid',rid). ThreadInvalidate(tid,pid,FlushList)

## 5.2.4 Processors

Each processor is modeled as a separate component (with a unique identity pid). Processors get and update the information of a region in a similar way as threads by using a set of send actions: s\_processorrequestinfo, s\_processornorefresh and s\_processorrefresh. How a processor reacts when it receives a *Data Return* message (modeled by r\_queue\_datareturn) is specified in Table 7. It first checks the last boolean parameter b in the message to find out whether this message is also a home node migration message. If that is the case, it will set itself as the home of the region. Otherwise, it updates the region's information according to the information contained in the message. How a processor reacts when it receives a a *Data Request* message (modeled by r\_queue\_datarequest) or a *Region Sponmigrate* message (modeled by r\_queue\_regionsponmigrate) is specified in Table 8. Processors deal with the *Flush Request* messages in a similar way.

Note the specification in Table 7 is slightly different from its corresponding part in the appendix, which has already contained a solution to a problem found during our analysis of the protocol. More explanation can be found in Section 6.2.

We recall that each processor maintains two message queues to store incoming messages. The HomeQueue is designed to buffer messages containing a request, while the RemoteQueue buffers messages containing a reply. To put a message into a queue, a *homequeue lock* or a *remotequeue lock* has to be obtained. The specifications of a HomeQueue and of a RemoteQueue are presented in Tables

Table 7

Specification of a processor dealing with a Data Return message

| <pre>Processor(pid:Processorld) = % The processor gets a Data Request message. % If it is not a home node migration message by checking not(b), % then update the information of the region according to r' % and set its home by the home of r'.  ∑tid:ThreadId ∑pid':Processorld ∑rid:RegionId ∑r':RegionInfo ∑b:Bool r_queue_datareturn(tid,pid,pid',rid,r',b). (∑r:RegionInfo s_processorrequestinfo(pid,rid,r). s_signal(tid,pid,rid). s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))). s_free_remotequeuelock(pid).Processor(pid) &lt; not(b) ▷ % Otherwise, update the writerlist of the region according to r', % set the its state as USED, and set its home by pid. ∑r:RegionInfo s_processorrequestinfo(pid,rid,r). s_signal(tid,pid,rid). s_processorrefresh(pid,rid, sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)). s_free_remotequeuelock(pid).Processor(pid)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | specification of a processor dealing with a Data rectain message                  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|

| <pre>% If it is not a home node migration message by checking not(b),<br/>% then update the information of the region according to r'<br/>% and set its home by the home of r'.<br/>∑tid:ThreadId ∑pid':ProcessorId ∑rid:RegionId ∑r':RegionInfo ∑b:Bool<br/>r_queue_datareturn(tid,pid,pid',rid,r',b).<br/>(∑r:RegionInfo s_processorrequestinfo(pid,rid,r).<br/>s_signal(tid,pid,rid).<br/>s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))).<br/>s_free_remotequeuelock(pid).Processor(pid)<br/>⊲ not(b) ▷<br/>% Otherwise, update the writerlist of the region according to r',<br/>% set the its state as USED, and set its home by pid.<br/>∑r:RegionInfo s_processorrequestinfo(pid,rid,r).<br/>s_signal(tid,pid,rid).<br/>s_processorrefresh(pid,rid,<br/>sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)).</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Processor(pid:ProcessorId) =                                                      |  |

| % then update the information of the region according to r'<br>% and set its home by the home of r'.<br>∑tid:ThreadId ∑pid':ProcessorId ∑rid:RegionId ∑r':RegionInfo ∑b:Bool<br>r_queue_datareturn(tid,pid,pid',rid,r',b).<br>(∑r:RegionInfo s_processorrequestinfo(pid,rid,r).<br>s_signal(tid,pid,rid).<br>s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))).<br>s_free_remotequeuelock(pid).Processor(pid)<br>⊲ not(b) ▷<br>% Otherwise, update the writerlist of the region according to r',<br>% set the its state as USED, and set its home by pid.<br>∑r:RegionInfo s_processorrequestinfo(pid,rid,r).<br>s_signal(tid,pid,rid).<br>s_processorrefresh(pid,rid,<br>sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | % The processor gets a Data Request message.                                      |  |

| % and set its home by the home of r'.<br>$\sum_{tid:ThreadId} \sum_{pid':ProcessorId} \sum_{rid:RegionId} \sum_{r':RegionInfo} \sum_{b:Bool} r_queue_datareturn(tid,pid,pid',rid,r',b).$ $(\sum_{r:RegionInfo} s_processorrequestinfo(pid,rid,r).$ $s_signal(tid,pid,rid).$ $s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))).$ $s_free\_remotequeuelock(pid).Processor(pid)$ $\triangleleft not(b) \triangleright$ % Otherwise, update the writerlist of the region according to r',<br>% set the its state as USED, and set its home by pid.<br>$\sum_{r:RegionInfo} s\_processorrequestinfo(pid,rid,r).$ $s\_signal(tid,pid,rid).$ $s\_processorrefresh(pid,rid, sethome(setstate(r')),USED),pid)).$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | % If it is not a home node migration message by checking not(b),                  |  |

| $ \begin{array}{l} \sum_{\text{tid:ThreadId } \sum_{\text{pid':ProcessorId } \sum_{\text{rid:RegionId } \sum_{r':RegionInfo } \sum_{b:Bool} \\ r\_queue\_datareturn(tid,pid,pid',rid,r',b). \\ (\sum_{r:RegionInfo} s\_processorrequestinfo(pid,rid,r). \\ s\_signal(tid,pid,rid). \\ s\_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))). \\ s\_free\_remotequeuelock(pid).Processor(pid) \\ \lhd not(b) \rhd \\ \% \text{ Otherwise, update the writerlist of the region according to r', \\ \% \text{ set the its state as USED, and set its home by pid.} \\ \sum_{r:RegionInfo} s\_processorrequestinfo(pid,rid,r). \\ s\_signal(tid,pid,rid). \\ s\_processorrefresh(pid,rid, \\ s\_toreessorrefresh(pid,rid, \\ sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)). \\ \end{array} $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | % then update the information of the region according to r'                       |  |

| <pre>r_queue_datareturn(tid,pid,pid',rid,r',b).<br/>(∑<sub>r:RegionInfo</sub> s_processorrequestinfo(pid,rid,r).<br/>s_signal(tid,pid,rid).<br/>s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))).<br/>s_free_remotequeuelock(pid).Processor(pid)<br/>&lt; not(b) ▷<br/>% Otherwise, update the writerlist of the region according to r',<br/>% set the its state as USED, and set its home by pid.<br/>∑<sub>r:RegionInfo</sub> s_processorrequestinfo(pid,rid,r).<br/>s_signal(tid,pid,rid).<br/>s_processorrefresh(pid,rid,<br/>sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)).</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | % and set its home by the home of r'.                                             |  |

| <pre>s_signal(tid,pid,rid). s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))). s_free_remotequeuelock(pid).Processor(pid) <pre></pre> </pre> <pre></pre> <pre< th=""><th></th><th></th></pre<>                                                                                             |                                                                                   |  |

| <pre>s_signal(tid,pid,rid). s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))). s_free_remotequeuelock(pid).Processor(pid) <pre></pre> </pre> <pre></pre> <pre< th=""><th><math>\left(\sum_{r:\text{RegionInfo}} \text{s_processorrequestinfo(pid,rid,r}\right)</math></th><th></th></pre<> | $\left(\sum_{r:\text{RegionInfo}} \text{s_processorrequestinfo(pid,rid,r}\right)$ |  |

| <pre>s_free_remotequeuelock(pid).Processor(pid)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                   |  |

| <pre>     <pre>         <pre>             <pre></pre></pre></pre></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | s_processorrefresh(pid,rid,sethome(setstate(r,getstate(r')),gethome(r'))).        |  |

| <pre>% Otherwise, update the writerlist of the region according to r',<br/>% set the its state as USED, and set its home by pid.</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | s_free_remotequeuelock(pid).Processor(pid)                                        |  |

| % set the its state as USED, and set its home by pid.<br>$\sum_{r:RegionInfo} s\_processorrequestinfo(pid,rid,r).$ $s\_signal(tid,pid,rid).$ $s\_processorrefresh(pid,rid,$ $s=thome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)).$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $\triangleleft not(b) \vartriangleright$                                          |  |

| <pre>\sum_{r:RegionInfo} s_processorrequestinfo(pid,rid,r). s_signal(tid,pid,rid). s_processorrefresh(pid,rid, sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)).</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | % Otherwise, update the writerlist of the region according to r',                 |  |

| s_signal(tid,pid,rid).<br>s_processorrefresh(pid,rid,<br>sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | % set the its state as USED, and set its home by pid.                             |  |

| s_signal(tid,pid,rid).<br>s_processorrefresh(pid,rid,<br>sethome(setstate(setwriterlist(r,getwriterlist(r')),USED),pid)).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\sum_{r:\text{RegionInfo}}$ s_processorrequestinfo(pid,rid,r).                   |  |